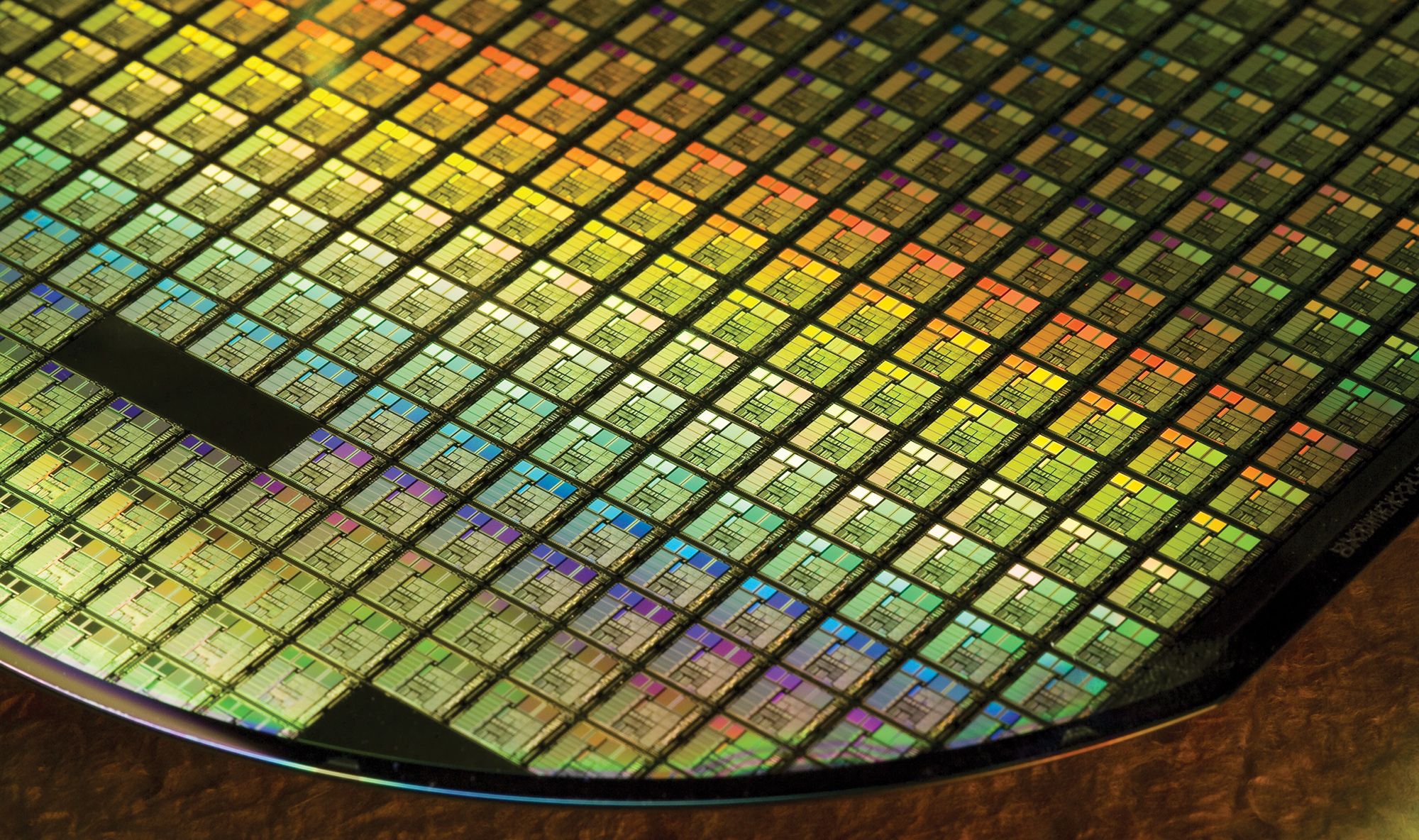

Le fondeur taiwanais TSMC doit son succès à sa capacité à proposer rapidement les noeuds de gravure les plus fins, quitte à prendre quelques raccourcis pour gagner du temps sur la concurrence avant d'exploiter pleinement les technologies nécessaires.

Il sera ainsi en mesure de lancer rapidement la gravure en 3 nm en restant sur des transistors 3D FinFET quand Samsung sera un peu plus long à proposer sa technique reposant pour sa part sur du GAAFET.

C'est ensuite sur le 2 nm que TSMC passera au GAAFET mais déjà se profile un noeud de gravure encore plus bas. Selon le Business Korea, la firme annoncera durant le mois de juin la transition de ses équipes de R&D vers la gravure en 1,4 nm., ce qui devrait une nouvelle fois lui permettre de couper l'herbe sous le pied de son concurrent Samsung.

Toujours plus fin, toujours plus cher

Le fondeur taiwanais cherche à maintenir sa part de marché à plus de 50% et surtout à conserver ses plus gros clients capables de commander des dizaines de millions de puces dans les gravures les plus fines, seul moyen de rentabiliser les énormes investissements consentis.

Mais si TSMC veut se montrer si précoce, c'est peut-être aussi du fait de la roadmap d'Intel qui envisage de passer à la gravure en 2 nm (Intel 20A) dès 2024 puis en 1,8 nm (Intel 18A) vers 2025.

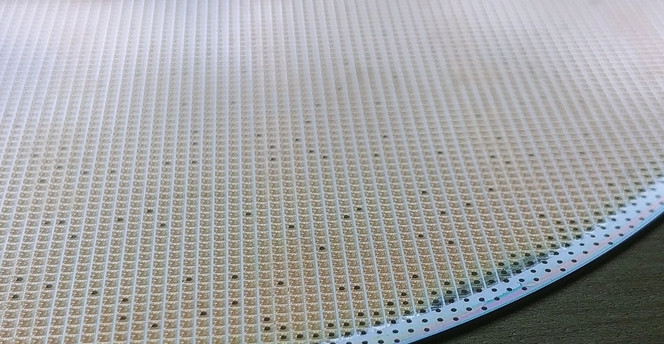

Toutefois, il reste à voir jusqu'où cette fuite en avant pourra aller. Les investissements sont toujours plus élevés avec une complexité croissante et des rendements de plus en plus difficile à maîtriser à mesure que la technique se rapproche des limites naturelles.