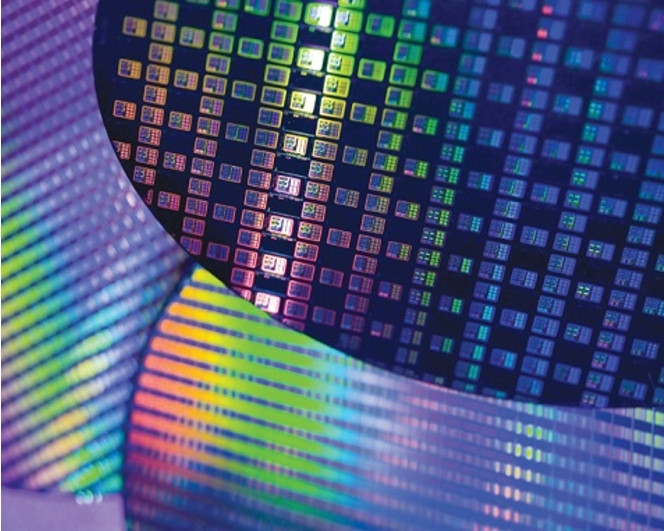

Depuis son passage au 7 nm avec quelques trimestres d'avance sur son concurrent Samsung (et pendant qu'Intel a mis beaucoup de temps à finaliser sa gravure en 10 nm, retardant aussi le 7 nm), le fondeur taiwanais TSMC est engagé dans une course de vitesse pour rester le premier sur les noeuds de plus en plus fins et conserver les gros clients capables de commander des dizaines ou centaines de millions de puces.

Le secteur des semiconducteurs constituant un enjeu national stratégique, la firme a annoncé de lourds investissements (100 milliards de dollars) ces prochaines années à la fois pour améliorer ses capacités de production et contribuer à réduire la pénurie actuelle de semiconducteurs, mais aussi pour continuer de soutenir sa puissante R&D et préparer l'avenir.

Déjà en mesure de produire des composants gravés en 5 nm, les prochaines étapes concerneront le passage au 4 nm puis au 3 nm, avec des astuces pour rester le premier à atteindre une telle finesse.

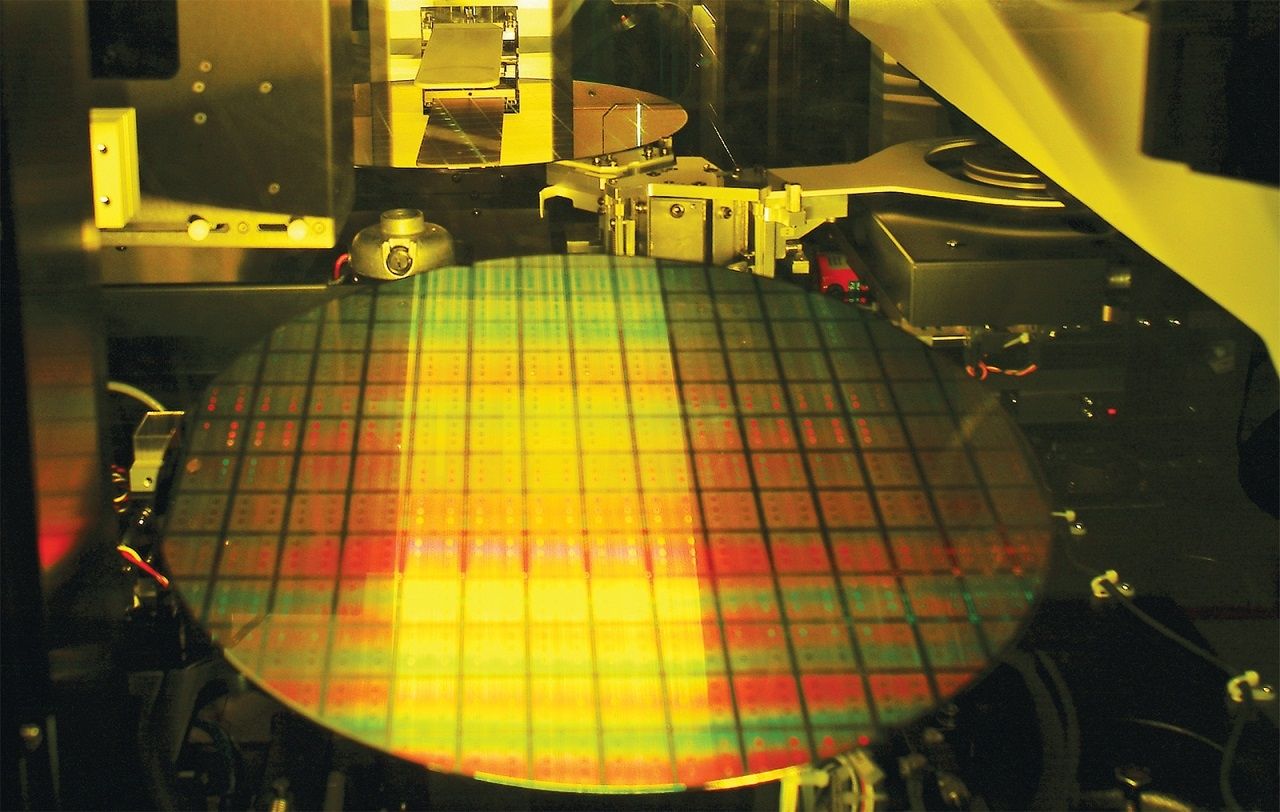

Le savoir-faire acquis sur la gravure en 5 nm va permettre à TSMC de proposer une évolution légère sous la forme de la gravure en 4 nm dès l'an prochain, après une phase de pré-production fin 2021.

Elle apportera des améliorations de performances et de consommation d'énergie sur un noeud qui sera alors mature et donc moins onéreux pour les clients.

En 2022 aussi commencera à arriver la gravure en 3 nm. Chez TSMC, elle exploitera toujours les transistors 3D FinFET, ce qui permettra une nouvelle fois de gagner du temps sur Samsung qui exploitera pour sa part une nouvelle technologie GAAFET (Gate All Around).

Cela devrait tout de même fournir 10 à 15% de performances en plus par rapport au 5 nm ou de 20 à 25% de réduction de consommation d'énergie, selon le critère de comparaison retenu, indique le site AnandTech.

Le GAAFET à partir de la gravure en 2 nm

Ce choix permettra de réutiliser une partie des équipements de production existant, constituant là aussi un gain de temps pour la mise en service. La gravure en 3 nm de TSMC sera donc elle aussi un dérivé de la gravure en 5 nm et continuera d'intéresser aussi bien les processeurs mobiles que pour pour HPC.

Ce n'est qu'ensuite, pour préparer la gravure en 2 nm, que TSMC passera au GAAFET. Mais ceci est encore une question de recherche et développement. C'est là qu'il sera intéressant de voir si Samsung, qui aura basculé sur cette technologie dès le noeud en 3 nm, pour profiter d'une certaine expérience accumulée pour tenter de reprendre l'avantage.